Frank,

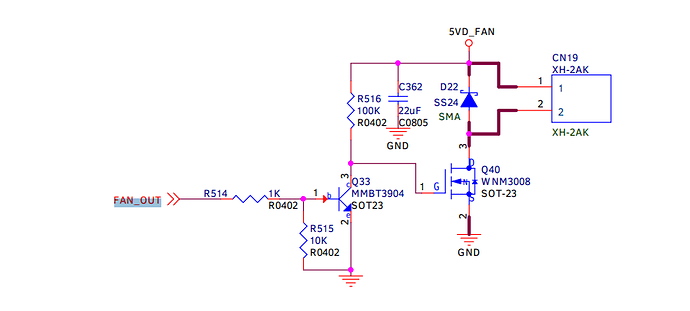

I am beginning to get some handle on understanding the DTS entries for pio/pwm1-2-pins node, pwm node in mt7622-bananapi-bpi-r64.dts.

I looked at the commit you pointed to above (b14047742a29e6c05c212ccf12de415590bac090). I understand to recompile the DTS using pwm3_pins in mt7622-bananapi-bpi-r64.dts, like so:

&pwm {

pinctrl-names = "default";

/* pinctrl-0 = <&pwm7_pins>; */

pinctrl-0 = <&pwm3_pins>;

status = "okay";

};

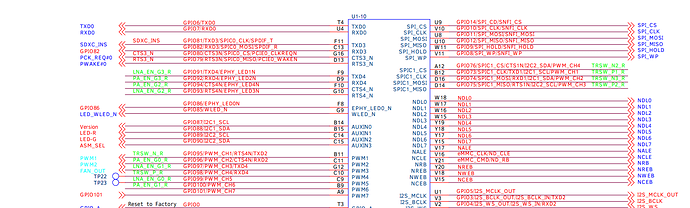

But I am confused about one thing: pwm_ch3 has three modes, as can be seen in drivers/pinctrl/mediatek/pinctrl-mt7622.c

static int mt7622_pwm_ch3_0_pins[] = { 53, };

static int mt7622_pwm_ch3_0_funcs[] = { 3, };

static int mt7622_pwm_ch3_1_pins[] = { 75, };

static int mt7622_pwm_ch3_1_funcs[] = { 4, };

static int mt7622_pwm_ch3_2_pins[] = { 97, };

static int mt7622_pwm_ch3_2_funcs[] = { 0, };

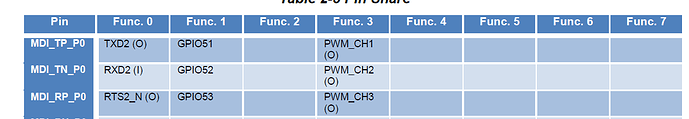

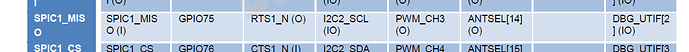

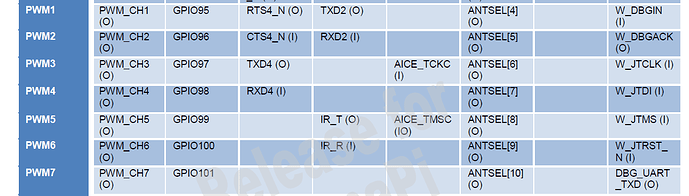

which I interpret to pwm_ch3 is driven to GPIO97 for function mode 0, it is driven to GPIO75 in function mode 4 and to GPIO53 in function mode 3. This matches with the table 2.5 in “section 2.3.1 Pin share scheme” in the MT7622A_Datasheet_for_BananaPi_Only(1).pdf

So my question is: when I replace pwm7_pins with pwm3_pins with the definition

pwm3_pins: pwm3-pins {

mux {

function = "pwm";

groups = "pwm_ch3_0"; /*mt7622_pwm_ch3_0_pins[] = { 53, };*/

};

};

The PWM3 will be driven to GPIO53 correct?

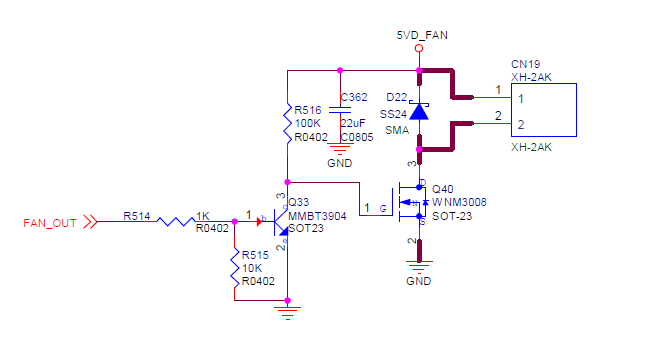

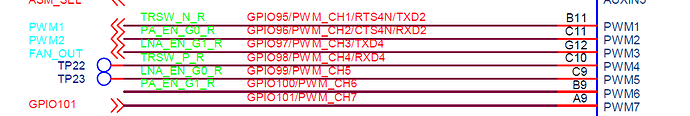

Whereas in the schematic, the FAN_OUT is connected to GPIO97

So I am wondering if we should use groups = “pwm_ch3_2”

In fact, I would say, instead of using groups = “pwm_chX_0” for pwmX_pins, it should be “pwm_chX_2” (for pwm 1,2,3,5,7) or “pwm_chX_3” (for pwm 4,6) to get the PWM generated on GPIO95…GPIO101

and need only know how to define the pwm-node to use all pwms without changing the pwm-node itself everytime. in 4.19 i tried defining subnodes which seems to be wrong…maybe the right way is defining only multiple pinctrl-x like this (default have to be there as stated in documentation, so i set name of first=pwm1 to default)

and need only know how to define the pwm-node to use all pwms without changing the pwm-node itself everytime. in 4.19 i tried defining subnodes which seems to be wrong…maybe the right way is defining only multiple pinctrl-x like this (default have to be there as stated in documentation, so i set name of first=pwm1 to default)