Bluetooth-issue is solved by increased sleep in SCPSYS-driver Banana Pi BPI-R64 open source router with MTK MT7622 64 bit chip design

gpio-issue is solved by disabling i2c1 (which shares pin on gpio-header): Banana Pi BPI-R64 open source router with MTK MT7622 64 bit chip design

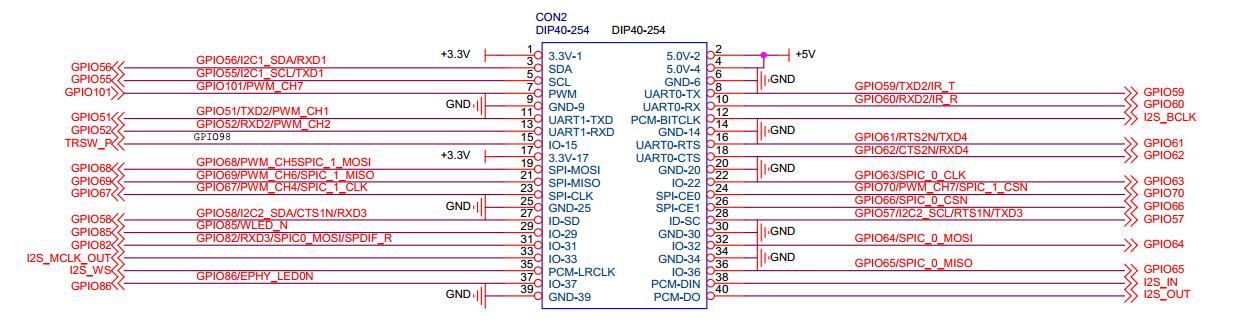

which uart is debug-uart? this looks like uart0, but looking on gpio-header (there are uart0+1) suggests uart2 as debug-uart like on r2

in dts uart1 is completely missing…i see uart1 in mt7622.dtsi which is included, but maybe i miss uart1_pins which is defined for the other 2 in dts

uart0_pins: uart0-pins {

mux {

function = "uart";

groups = "uart0_0_tx_rx" ;

};

};

uart2_pins: uart2-pins {

mux {

function = "uart";

groups = "uart2_1_tx_rx" ;

};

};

why is uart2=uart2_1_tx_rx (what does the 1 mean)?

if i look into drivers/pinctrl/mediatek/pinctrl-mt7622.c i see:

PINCTRL_PIN_GROUP("uart0_0_tx_rx", mt7622_uart0_0_tx_rx),

PINCTRL_PIN_GROUP("uart1_0_tx_rx", mt7622_uart1_0_tx_rx),

PINCTRL_PIN_GROUP("uart1_0_rts_cts", mt7622_uart1_0_rts_cts),

PINCTRL_PIN_GROUP("uart1_1_tx_rx", mt7622_uart1_1_tx_rx),

PINCTRL_PIN_GROUP("uart1_1_rts_cts", mt7622_uart1_1_rts_cts),

PINCTRL_PIN_GROUP("uart2_0_tx_rx", mt7622_uart2_0_tx_rx),

PINCTRL_PIN_GROUP("uart2_0_rts_cts", mt7622_uart2_0_rts_cts),

PINCTRL_PIN_GROUP("uart2_1_tx_rx", mt7622_uart2_1_tx_rx),

PINCTRL_PIN_GROUP("uart2_1_rts_cts", mt7622_uart2_1_rts_cts),

PINCTRL_PIN_GROUP("uart2_2_tx_rx", mt7622_uart2_2_tx_rx),

for uart1 i have uart1_0_tx_rx and uart1_1_tx_rx…which one is the right one?

static int mt7622_uart0_0_tx_rx_pins[] = { 6, 7, };//not matching gpio-number (=59,60) => maybe the debug-uart?

...

static int mt7622_uart1_0_tx_rx_pins[] = { 55, 56, };

static int mt7622_uart1_1_tx_rx_pins[] = { 73, 74, };

...

static int mt7622_uart2_1_tx_rx_pins[] = { 51, 52, }; //=gpio-numbers of uart1

no uart1_x_tx_rx does match gpio-numbers of uart0 on gpio-header (uart1 on gpio=uart2 in dts)

If these numbers are the gpios i guess uart1 (uart0 on gpioheader) should use this:

static int mt7622_uart2_2_tx_rx_pins[] = { 59, 60, };

i can confirm that debug-uart is the uart0 from dts…if i disable it i get no console-output after ATF-infos

## Booting kernel from Legacy Image at 44000000 ...

Image Name: Linux Kernel 4.19.0-r64-main

Image Type: ARM Linux Kernel Image (uncompressed)

Data Size: 8527880 Bytes = 8.1 MiB

Load Address: 40080000

Entry Point: 40080000

Verifying Checksum ... OK

## Flattened Device Tree blob at 47000000

Booting using the fdt blob at 0x47000000

Loading Kernel Image ... OK

Loading Device Tree to 5cf02000, end 5cf0a835 ... OK

Starting kernel ...

[ATF][ 6.145169]save kernel info

[ATF][ 6.148370]Kernel_EL2

[ATF][ 6.151127]Kernel is 64Bit

[ATF][ 6.154314]pc=0x40080000, r0=0x5cf02000, r1=0x0

INFO: BL3-1: Preparing for EL3 exit to normal world, Kernel

INFO: BL3-1: Next image address = 0x40080000

INFO: BL3-1: Next image spsr = 0x3c9

[ATF][ 6.172581]el3_exit

no output after that, but device boots and i can access via ssh

any idea on preloader for emmc?

is there a driver for soc-internal bgn-wifi (https://www.mediatek.com/products/homeNetworking/mt7622)?

for pwm i defined this:

pwm1_pins: pwm1-2-pins {

mux {

function = "pwm";

groups = "pwm_ch1_0";/* mt7622_pwm_ch1_0_pins[] = { 51, }; */

};

};

pwm2_pins: pwm1-2-pins {

mux {

function = "pwm";

groups = "pwm_ch2_0"; /*mt7622_pwm_ch2_0_pins[] = { 52, };*/

};

};

pwm4_pins: pwm1-2-pins {

mux {

function = "pwm";

groups = "pwm_ch4_1"; /*mt7622_pwm_ch4_1_pins[] = { 67, };*/

};

};

pwm5_pins: pwm1-2-pins {

mux {

function = "pwm";

groups = "pwm_ch5_0"; /*mt7622_pwm_ch5_0_pins[] = { 68, };*/

};

};

pwm6_pins: pwm1-2-pins {

mux {

function = "pwm";

groups = "pwm_ch6_0"; /*mt7622_pwm_ch6_0_pins[] = { 69, };*/

};

};

pwm7_pins: pwm1-2-pins {

mux {

function = "pwm";

groups = "pwm_ch7_2";

};

};

&pwm {

pinctrl-names = "default";

status = "okay";

pwm1 {

pinctrl-0 = <&pwm1_pins>;

};

pwm2 {

pinctrl-0 = <&pwm2_pins>;

};

pwm4 {

pinctrl-0 = <&pwm4_pins>;

};

pwm5 {

pinctrl-0 = <&pwm5_pins>;

};

pwm6 {

pinctrl-0 = <&pwm6_pins>;

};

pwm7 {

pinctrl-0 = <&pwm7_pins>;

};

};

is that right? it compiles  and i see nodes in sysfs:

and i see nodes in sysfs:

/sys/firmware/devicetree/base/pwm@11006000/pwm7

/sys/firmware/devicetree/base/pwm@11006000/pwm5

/sys/firmware/devicetree/base/pwm@11006000/pwm1

/sys/firmware/devicetree/base/pwm@11006000/pwm6

/sys/firmware/devicetree/base/pwm@11006000/pwm4

/sys/firmware/devicetree/base/pwm@11006000/pwm2

but gpio101 is not blocked as i expected, so i guess its is not working

maybe this is related: https://patchwork.kernel.org/project/linux-mediatek/list/?series=68207 but as far as i see it only maps the clocks and do not register a new pincontrol to subnode

for r2 pwm is defined like this (with constants, also only 1 pwm-node + 1 pin-define):

pwm_pins_a: pwm-default {

pins-pwm {

pinmux = <MT7623_PIN_203_PWM0_FUNC_PWM0>,

<MT7623_PIN_204_PWM1_FUNC_PWM1>,

<MT7623_PIN_205_PWM2_FUNC_PWM2>,

<MT7623_PIN_206_PWM3_FUNC_PWM3>,

<MT7623_PIN_207_PWM4_FUNC_PWM4>;

};

};

but how to do this for r64, which has complete different pin-define?

and i see nodes in sysfs:

and i see nodes in sysfs: