Hi everyone I can’t find the full schematic of this product I can’t find about DDR4 circuit and power circuit part and the blocked part about mt7988a where can I find this?

Hi frank-w

https://drive.google.com/drive/folders/1XiVchy0a4syYFVlTndhVCETNJ9x7KOYi?usp=sharing There is no DDR4 connection block in the schematic on this link and there are no 1 to 3 pages and 14 to 16 pages Thank you

You’re right,but i’m not allowed to share the missing pages. @simon @zuowei8 @sinovoip whats the reason for removing these pages?

This information in wrong in the specification of the R4 board.

Supported interface modes for the SFP+ cages of the R4 are: SGMII, 1000Base-X, 2500Base-X, 5GBase-R, 10GBase-R, USXGMII

So yes, also 1.25Gbps (= 1000Base-X or SGMII) and 3.125Gbps (= 2500Base-X) SFP modules can work fine with the R4.

Hi @dangowrt . Thanks for this clarification. Because I’m looking to replace my current PCEngines APU6 AMD GX-412TC SOC. Looking to Banana Pi BPI-R4 in Wiki is written here: Getting Started with BPI-R4 - Banana Pi Wiki : “The SFP serdes speed of BPI-R4 is fixed at 10Gbps, so only SFP that support this can be used!”. For me was very confusing this information because I need to use 1GbE fiber SFP to connect to the ISP. But the LAN is on 10GbE.

There are some tests done to prove this working setup? I don’t want to pay for the board and not able to use it with 1GbE SFP.

I’ve tried multiple 2500MBit/s and 1000MBit/s SFP modules during testing. With the exception of TL-SM410U (which requires power to be present before indicating module presence) they all work fine.

It is really important to use the search:

And for the understanding: What banana pi on getting started delivered, is for their special “limited” open WRT Version. dangowrt is developing the openwrt System which will end in an official support (hoping is good enough explained).

But the system for BPI-R4 is still under development. I’m a bit afraid (give it a try) that you are looking for a finished WiFI 7 router without bugs … . But you’re welcome ![]() !

!

@Lorem_amicus , I’ve searched the forum and I found some threads. But also, as a new user of BPI, I found too many contradictory information, mainly in Wiki (I’ve already specify what was the main contradictory information in a previous reply). That’s why I wanted to ask first to be sure that others already test it with 1Gbit SFP Optical or Copper to not have a surprise when I’m getting the board and is not working.

Regarding your comments about the support, I’m aware that are some limitations yet. I worked on an Odroid C2 / XU4 and I was able to build U-boot UEFI + GRUB to boot Debian Linux. Originally Armbian is coming with U-boot → Kernel booting solution. I have a whole thread on Armbian or Hardkernel about this solution. My Odroid-C2 is still working these days with U-boot UEFI + GRUB. Of course I need to apply some patches to grub-mkconfig to install devicetree when Kernel is booting, because GRUB doesn’t have any support for DTB.

I like more to have GRUB as a second bootloader to be able to choose which Kernel I want to boot. I want to use it mainly as wired router, not as WiFi router. My WiFi is already configured with Unifi WiFi devices.

What I need is to use it with a Debian Linux distribution + FRRouting and more network power than my actual AMD GX-412TC SOC can handle. I’m having VRFs and route-leaks + VPNs.

My current router is getting bottlenecks around 800-1000Mbps without NAT, just simple routing.

Okay, you know what you are doing!

Could you please document what is open source hardware and what is not?

17 days go, I have kindly asked the same question. Sadly, my question was ignored and now I can only assume that, based on what I have seen so far, the BPI-R4 is not open source hardware. In fact only parts of it’s hardware designs are covered, most notably the main processor ISA is closed.

Transparency is key open source hardware products and communities. I’m not making this up, to quote the Open Source Hardware (OSHW) Definition 1.0

- Documentation

The hardware must be released with documentation including design files, …

- Scope

The documentation for the hardware must clearly specify what portion of the design, if not all, is being released under the license.

The question is not ignored…there was nobody yet who can answer it…i avoid answering that i do not know it.

Imho this can only be answered by bpi team itself or mtk,but i guess you’re right that the SoC itself is closed source

The question is not ignored…there was nobody yet who can answer it…i avoid answering that i do not know it.

Thanks frank-w for this promp follow up, I understand the situation better now.

Imho this can only be answered by bpi team itself or mtk,but i guess you’re right that the SoC itself is closed source

I understand that each chip manufacturer would be able to tell about their own chip, but that would be a partial answer as I’m looking at BPI-R4 open source status, meaning where it starts, and where it ends. I don’t expect other chip manufacturer would have the required knowledge to fully answer the question.

I’ll eagerly wait @sinovoip answer, with other open source hardware enthusiasts. ![]()

Kind regards

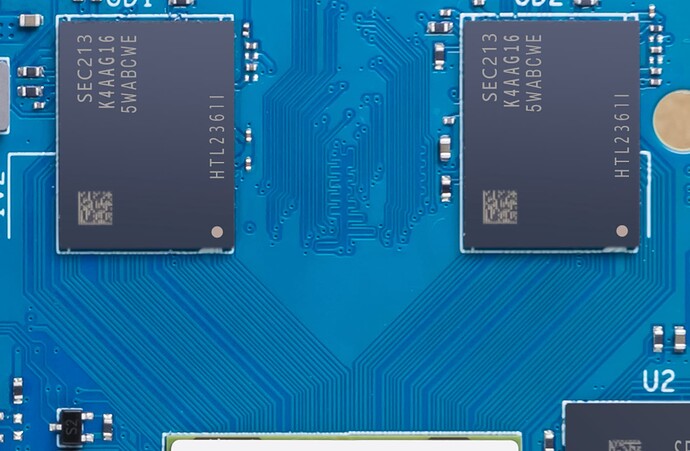

@simon I have one question regarding DRAM traces on board. I noticed, at least for DDR4, that many board route the circuits in a weird way, this is apparently to make them same length and improve stability.

On R4 I don’t see this pattern, is it achieved in another way?

only need to make the clk traces equal in length, and have DQ calibration for data traces.

Hello everybody,

do we know if the current BPI-R4 revision is the last? I read something about when using the NVMe port one of the sfp+ ports doesn’t work correctly. Is that fixed?

Afair this is fixed in last version (1.2) and nvme put the i2c down so both sfp and the other devices connected to the same i2c are not usable (eeprom,rtc).

But have not this version

So that’s for before 1.2 revision?

Sorry but I haven’t heard about a revision 1.2. If someone has information about “Rev 1.2” please share it!

For me the case was solved:

You can tape off these 2 pins:

or desolder these two resistors:

Because this is a development board (not for end consumers), it make sense for me there will never be revision 1.2. But may be I’m wrong?

Thought v1.2 is done with fixing this pcie issue (removing the 2 reistors) ,but can be wrong. I only have till v1.1 and taped the 2 pins.