Hi garywang,

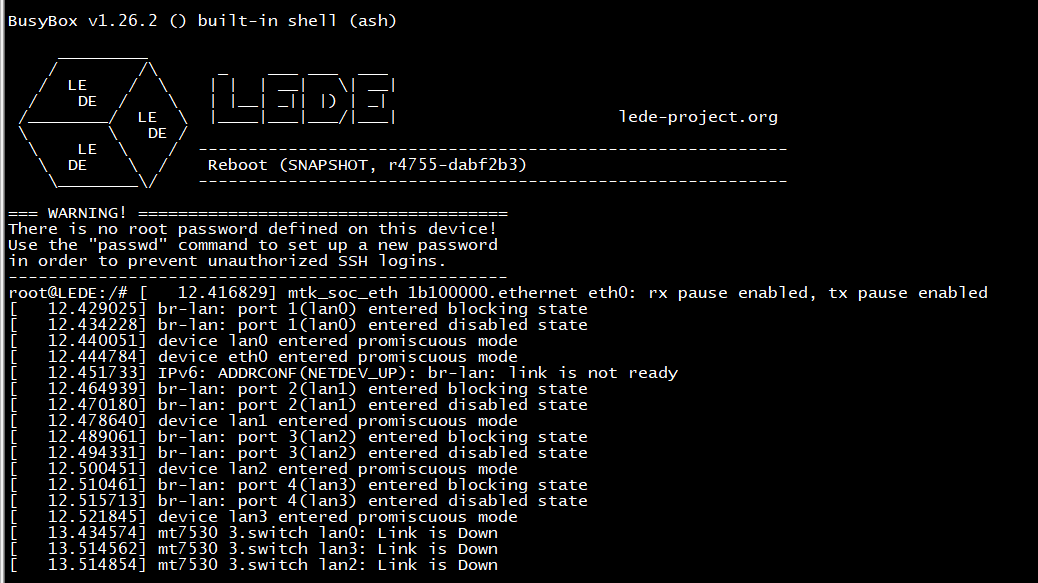

i have done all steps above. Kernel boots but stucks at “mtk_soc_eth 1b100000.ethernet eth1: rx pause enabled, tx pause enabled”.

Board init log:

`[USBD] USB PRB0 LineState: 0

[USBD] USB cable/ No Cable inserted!

[PLFM] Keep stay in USB Mode

Platform initialization is ok

wait for frequency meter finish, CLK26CALI = 0x81

mt_pll_post_init: mt_get_cpu_freq = 1040000Khz

wait for frequency meter finish, CLK26CALI = 0x90

mt_pll_post_init: mt_get_bus_freq = 273000Khz

wait for frequency meter finish, CLK26CALI = 0x81

mt_pll_post_init: mt_get_mem_freq = 133250Khz

[PWRAP] pwrap_init_preloader

[PWRAP] pwrap_init

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=0,rdata=2D52

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=1,rdata=2D52

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=2,rdata=2D52

[PWRAP] _pwrap_init_sistrobe [Read Test] pass,index=3 rdata=5AA5

[PWRAP] _pwrap_init_sistrobe [Read Test] pass,index=4 rdata=5AA5

[PWRAP] _pwrap_init_sistrobe [Read Test] pass,index=5 rdata=5AA5

[PWRAP] _pwrap_init_sistrobe [Read Test] pass,index=6 rdata=5AA5

[PWRAP] _pwrap_init_sistrobe [Read Test] pass,index=7 rdata=5AA5

[PWRAP] _pwrap_init_sistrobe [Read Test] pass,index=8 rdata=5AA5

[PWRAP] _pwrap_init_sistrobe [Read Test] pass,index=9 rdata=5AA5

[PWRAP] _pwrap_init_sistrobe [Read Test] pass,index=10 rdata=5AA5

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=11,rdata=B54B

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=12,rdata=B54B

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=13,rdata=B54B

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=14,rdata=B54B

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=15,rdata=B54B

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=16,rdata=B54B

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=17,rdata=B54B

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=18,rdata=B54B

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=19,rdata=6A97

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=20,rdata=6A97

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=21,rdata=6A97

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=22,rdata=6A97

[PWRAP] _pwrap_init_sistrobe [Read Test] fail,index=23,rdata=6A97

[PWRAP] _pwrap_init_reg_clock

[PMIC_WRAP]wrap_init pass,the return value=0.

[pmic6323_init] Preloader Start..................

[pmic6323_init] PMIC CHIP Code = 0x2023

INT_MISC_CON: 1 TOP_RST_MISC: 1

pl pmic powerkey Release

[pmic6323_init] powerKey = 0

[pmic6323_init] is USB in = 0xB004

[pmic6323_init] Reg[0x11A]=0x1B

pmic setup LED

[pmic6323_init] Done...................

mt7623 disable long press reset ->>>>>

mt7623 disable long press reset <<<<<-

mt7623 VPA supplied by 1.0V to MT7530 ->

mt7623 VPA supplied by 1.0V to MT7530 <-

mt7623 enables RG_VGP1_EN for LCM ->

mt7623 enables RG_VGP1_EN for LCM <-

MT7623 E2 setting =>

MT7623 E2 setting <=

[PLFM] Init I2C: OK(0)

[PLFM] Init PWRAP: OK(0)

[PLFM] Init PMIC: OK(0)

[PLFM] chip[CA00]

[BLDR] [Support SD/eMMC] Build Time: 20170905-120917

==== Dump RGU Reg ========

RGU MODE: 4D

RGU LENGTH: FFE0

RGU STA: 0

RGU INTERVAL: FFF

RGU SWSYSRST: 0

==== Dump RGU Reg End ====

RGU: g_rgu_satus:0

mtk_wdt_mode_config mode value=10, tmp:22000010

PL P ON

WDT does not trigger reboot

RGU mtk_wdt_init:MTK_WDT_DEBUG_CTL(590200F3)

kpd read addr: 0x0040: data:0x4001

Enter mtk_kpd_gpio_set!

kpd debug column : 0, 0, 0, 0, 0, 0, 0, 0

kpd debug row : 0, 0, 0, 0, 0, 0, 0, 0

after set KP enable: KP_SEL = 0x0 !

MTK_PMIC_RST_KEY is used for this project!

[RTC] get_frequency_meter: input=0x0, ouput=5

[RTC] get_frequency_meter: input=0x0, ouput=3968

[RTC] get_frequency_meter: input=0x0, ouput=5

[RTC] get_frequency_meter: input=0x0, ouput=0

[RTC] get_frequency_meter: input=0x0, ouput=0

[RTC] bbpu = 0xD, con = 0x426

[RTC] powerkey1 = 0xA357, powerkey2 = 0x67D2

Writeif_unlock

[RTC] RTC_SPAR0=0x40

rtc_2sec_reboot_check cali=1792

rtc_2sec_stat_clear

[RTC] irqsta = 0x0, pdn1 = 0x0, pdn2 = 0x201, spar0 = 0x40, spar1 = 0x800

[RTC] new_spare0 = 0x0, new_spare1 = 0x1, new_spare2 = 0x1, new_spare3 = 0x1

[RTC] bbpu = 0xD, con = 0x426, cali = 0x700

pl pmic powerkey Release

[PLFM] Power key boot!

[RTC] rtc_bbpu_power_on done

[EMI] mcp_dram_num:0,discrete_dram_num:1,enable_combo_dis:0

[EMI] PCDDR3

[Check]mt_get_mdl_number 0x0

[EMI] eMMC/NAND ID = 0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0

[EMI] MDL number = 0

[EMI] emi_set eMMC/NAND ID = 0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0

[EMI][Vcore]0x21E=0x48,0x220=0x48

[EMI][Vmem]0x554=0x0

wait for frequency meter finish, CLK26CALI = 0x81

[EMI] PCDDR3 DRAM Clock = 1599912 KHz, MEMPLL MODE = 2

[EMI] PCDDR3 RXTDN Calibration:

Start REXTDN SW calibration...

drvp=0xB,drvn=0x9

[EMI] pinmux = 4

===============================================================================

dramc_write_leveling_swcal

===============================================================================

delay byte0 byte1 byte2 byte3

-----------------------------

0 0 0 0 1

1 0 0 0 1

2 0 0 1 1

3 0 1 1 1

4 0 1 1 1

5 0 1 1 1

6 0 1 1 1

7 0 1 1 1

8 0 1 1 1

9 1 1 1 1

10 1 1 1 1

11 1 1 1 1

12 1 1 1 1

13 1 1 1 1

14 1 1 1 1

15 1 1 1 1

pass bytecount = 4

byte_i status best delay

0 2 9

1 2 3

2 2 2

3 2 0

========================================

[write leveling]DQS: 0x239, DQM: 0x239

[write leveling after remap]DQ byte0 reg: 0x200 val: 0x99993333

[write leveling after remap]DQ byte1 reg: 0x204 val: 0x33339999

[write leveling after remap]DQ byte2 reg: 0x208 val: 0x22220000

[write leveling after remap]DQ byte3 reg: 0x20C val: 0x2222

=============================================

X-axis: DQS Gating Window Delay (Fine Scale)

Y-axis: DQS Gating Window Delay (Coarse Scale)

=============================================

0 8 16 24 32 40 48 56 64 72 80 88 96 104 112 120

--------------------------------------------------------------------------------

0000:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0001:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0002:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0003:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0004:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0005:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0006:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0007:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0008:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0009:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000A:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000B:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000C:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000D:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000E:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000F:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0010:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1

0011:| 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1

0012:| 0 0 0 0 1 1 1 1 1 1 1 1 1 0 0 0

0013:| 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0

0014:| 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0

0015:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0016:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0017:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0018:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0019:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001A:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001B:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001C:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001D:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001E:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001F:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Rank 0 coarse tune value selection : 18, 18

18

64

rank 0 coarse = 18

rank 0 fine = 64

00:| 0 0 0 0 0 0 0 0 1 1 1 0

opt_dle value:13

==================================================================

RX DQS perbit delay software calibration

==================================================================

1.0-31 bit dq delay value

==================================================================

bit| 0 1 2 3 4 5 6 7 8 9

--------------------------------------

0 | 0 0 0 0 0 0 0 0 0 0

10 | 0 0 0 0 0 0 0 0 0 0

20 | 0 0 0 0 0 0 0 0 0 0

30 | 0 0

--------------------------------------

==================================================================

2.dqs window

x=pass dqs delay value (min~max)center

y=0-7bit DQ of every group

input delay:DQS0 =49 DQS1 = 39 DQS2 =51 DQS3 = 45

==================================================================

bit DQS0 bit DQS1 bit DQS2 bit DQS3

0 (20~68)44 8 (7~58)32 16 (21~67)44 24 (18~62)40

1 (21~70)45 9 (7~56)31 17 (21~68)44 25 (17~62)39

2 (21~70)45 10 (9~58)33 18 (23~68)45 26 (19~64)41

3 (20~67)43 11 (11~60)35 19 (21~67)44 27 (19~63)41

4 (21~74)47 12 (17~62)39 20 (24~74)49 28 (23~67)45

5 (22~67)44 13 (15~62)38 21 (23~67)45 29 (21~61)41

6 (23~69)46 14 (11~57)34 22 (22~72)47 30 (18~62)40

7 (26~73)49 15 (14~60)37 23 (29~74)51 31 (19~64)41

==================================================================

3.dq delay value last

==================================================================

bit| 0 1 2 3 4 5 6 7 8 9

--------------------------------------

0 | 5 4 4 6 2 5 3 0 7 8

10 | 6 4 0 1 5 2 7 7 6 7

20 | 2 6 4 0 5 6 4 4 0 4

30 | 5 4

==================================================================

*DQIDLY1 = 0x6040405

*DQIDLY2 = 0x30502

*DQIDLY3 = 0x4060807

*DQIDLY4 = 0x2050100

*DQIDLY5 = 0x7060707

*DQIDLY6 = 0x40602

*DQIDLY7 = 0x4040605

*DQIDLY8 = 0x4050400

*DRAMC_R0DELDLY = 0x2D332731

[MEM]CONA:F3A2,conf1:F07486A3

DM4BitMux = 1

DQSO 0 in TX per-bit = 2 <= DQSO 0 in WL = 9

DQSO 1 in TX per-bit = 0 <= DQSO 1 in WL = 3

[Warning] DQSO 2 in TX per-bit = 10 > DQSO 2 in WL = 2

[Warning] DQSO 3 in TX per-bit = 7 > DQSO 3 in WL = 0

Tx DQM dly = 0x1279

Tx DQM dly bit4 = 0x0

DRAMC_DQODLY1=79A98889h

DRAMC_DQODLY2=8966B99Bh

DRAMC_DQODLY3=12302112h

DRAMC_DQODLY4=22004345h

Tx DQ dly bit4 = 0x0

Tx DQS dly = 0x7A39

Tx DQS dly bit4 = 0x0

TX Byte0: DQ - 16, DQS - 17. win_sum= 32

TX Byte1: DQ - 21, DQS - 13. win_sum= 33

TX Byte2: DQ - 8, DQS - 22. win_sum= 29

TX Byte3: DQ - 9, DQS - 22. win_sum= 30

DRAMC calibration takes 651611583 CPU cycles

[EMI] DRAMC calibration passed

[MEM] complex R/W mem test pass

0:dram_rank_size:80000000

[Dram_Buffer] dram size:-2147483648

[Dram_Buffer] structure size: 1725560

[Dram_Buffer] MAX_TEE_DRAM_SIZE: 0

Load u-boot from eMMC...

[PLFM] Init Boot Device: OK(0)

[PART] blksz: 512B

[PART] [0x0000000000000000-0x000000000003FFFF] "PRELOADER" (512 blocks)

[PART] [0x0000000000000000-0x000000000003FFFF] "MBR" (512 blocks)

[PART] [0x0000000000040000-0x00000000000BFFFF] "UBOOT" (1024 blocks)

[PART] [0x00000000000C0000-0x00000000000FFFFF] "CONFIG" (512 blocks)

[PART] [0x0000000000100000-0x000000000013FFFF] "FACTORY" (512 blocks)

[PART] [0x0000000000140000-0x000000000213FFFF] "BOOTIMG" (65536 blocks)

[PART] [0x0000000002140000-0x000000000413FFFF] "RECOVERY" (65536 blocks)

[PART] [0x0000000004140000-0x000000004413FFFF] "ROOTFS" (2097152 blocks)

[PART] [0x0000000044140000-0x000001FFC413FFFF] "USER" (-4194304 blocks)

[platform_vusb_on] PASS

[TOOL] PMIC not dectect usb cable!

[TOOL] <UART> listen ended, receive size:0!

[TOOL] <UART> wait sync time 150ms->5ms

[TOOL] <UART> receieved data: ()

Device APC domain init setup:

bootloader load uboot ,the address of uboot is 81E00000

[PART]partition name UBOOT

[PART]partition start block 0x200

[PART]partition size 0x80000

[PART]partition blks 0x400

[PART]partition flags 0x0

[PART]partition name 0x8

[bean] part->startblk(0x200) bdev->blksz(0x200) part->part_id(8) hdr(0xFFB50000)

[BlkDev.c 101 ]partition block size 0x200 ,blks:0xE90000

[BlkDev.c 101 ]partition block erase size 0x200

[PART] load "UBOOT" from 0x0000000000050000 (dev) to 0x81E00000 (mem) [SUCCESS]

[PART] load speed: 10462KB/s, 300000 bytes, 28ms

[BT_SD_PG] device info 0x8590 0x8A00 0xCB01 0x102

0:dram_rank_size:80000000

[PLFM] md_type[0] = 100

[PLFM] md_type[1] = 32

[PLFM] boot reason: 0

[PLFM] boot mode: 0

[PLFM] META COM0: 0

[PLFM] <0xFFB7CC10>: 0x0

[PLFM] boot time: 2020ms

[PLFM] DDR reserve mode: enable = 0, success = 0

[BLDR] jump to 0x81E00000

[BLDR] <0x81E00000>=0xEA00000F

[BLDR] <0x81E00004>=0xE59FF014

U-Boot (Aug 01 2017 - 09:59:52)

================== Iverson debug. ===========================

g_nr_bank = 1.

g_total_rank_size = 0x80000000

DRAM: 2 GiB

WARNING: Caches not enabled

dev_num = 0

***size=4096, offset=1536, blk_start=3, blk_cnt=8

*** Warning - bad CRC, using default environment

In: serial

Out: serial

Err: serial

dev_num = 0

***size=4096, offset=1536, blk_start=3, blk_cnt=8

*** Warning - bad CRC, using default environment `

Next post contains Boot log.