- Background SoC: RK3568

Ethernet PHY: RTL8211F ×2 (RGMII interface)

MAC ↔ PHY connection: clock_in_out = “input” — the 125 MHz clock is provided from the PHY (CLKOUT) to the SoC.

DTS setting: Both gmac0 and gmac1 use clock_in_out = “input”.

- Issue Summary We’re seeing signal problems on the GMAC0 TXCLK pin (GPIO2_B0).

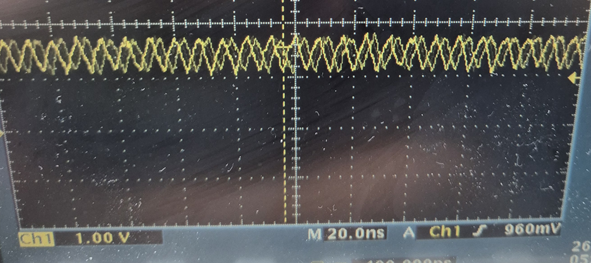

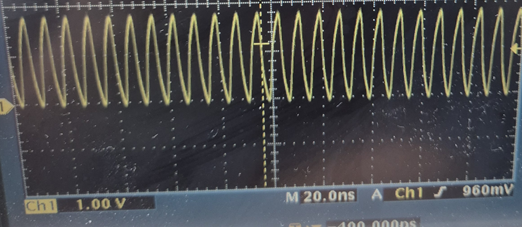

2.1 Problem Conditions When a 22Ω or 0Ω series resistor is added to TXC,

And we measure the waveform just before it exits the SoC,

The signal swings above an offset (e.g., around +1V ± 0.5V), not around 0V as expected.

Meanwhile, the RXC signal appears normal.

Drive Level Test Results drv_level_1: distorted waveform

From drv_level_5 and higher: waveform becomes normal only without the resistor

If a resistor is connected at TXC, even at drv_level_5, the signal starts swinging above an offset again.

We would appreciate any help or advice to resolve this issue.

Even if you set clock_in_out = "output", it works the same.

dts &gmac0 { assigned-clocks = <&cru SCLK_GMAC0_RX_TX>, <&cru SCLK_GMAC0>; assigned-clock-parents = <&cru SCLK_GMAC0_RGMII_SPEED>, <&gmac0_clkin>; clock_in_out = “input”;

pinctrl-names = "default";

pinctrl-0 = <

&gmac0_miim

&gmac0_tx_bus2

&gmac0_rx_bus2

&gmac0_rgmii_clk

&gmac0_rgmii_bus

&gmac0_clkinout

>;

phy-handle = <&rgmii_phy0>;

phy-mode = "rgmii";

snps,reset-gpio = <&gpio2 RK_PD1 GPIO_ACTIVE_LOW>;

snps,reset-active-low;

/* Reset time is 20ms, 100ms for rtl8211f */

snps,reset-delays-us = <0 20000 100000>;

tx_delay = <0x3c>;

rx_delay = <0x2f>;

status = "okay";

};

&gmac1 { assigned-clocks = <&cru SCLK_GMAC1_RX_TX>, <&cru SCLK_GMAC1>; assigned-clock-parents = <&cru SCLK_GMAC1_RGMII_SPEED>, <&gmac1_clkin>; clock_in_out = “input”;

pinctrl-names = "default";

pinctrl-0 = <

&gmac1m1_miim

&gmac1m1_tx_bus2

&gmac1m1_rx_bus2

&gmac1m1_rgmii_clk

&gmac1m1_rgmii_bus

&gmac1m1_clkinout

>;

phy-handle = <&rgmii_phy1>;

phy-mode = "rgmii";

snps,reset-gpio = <&gpio3 RK_PB0 GPIO_ACTIVE_LOW>;

snps,reset-active-low;

/* Reset time is 20ms, 100ms for rtl8211f */

snps,reset-delays-us = <0 20000 100000>;

tx_delay = <0x4f>;

rx_delay = <0x26>;

status = "okay";

};

&mdio0 { rgmii_phy0: phy@0 { compatible = “ethernet-phy-ieee802.3-c22”; reg = <0x0>; }; };

&mdio1 { rgmii_phy1: phy@0 { compatible = “ethernet-phy-ieee802.3-c22”; reg = <0x0>; }; };