This is more a question about the MT7988A SoC rather than the BPi-R4. I’m trying to figure out whether each of the two sets of USXGMII lanes from the SoC can support multiple downstream 1G ports. In other words, are these lanes USXGMII-S (supports only one 10G/5G/ … /10M), or USXGMII-M (supports up to one 10G / two 5G / ten 1G / … )? More info on USXGMII from Cisco here. If it turns out they’re USXGMII-M, then a managed Ethernet controller (like the Marvell 88E1780) could be used to combine multiple ports over the Serdes.

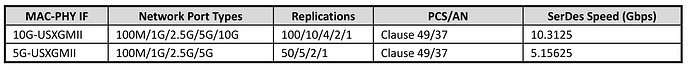

Section 8.5.1 from the MT7988A platform datasheet on the BPi-R4 info page has the following table -

The table clearly states that the 10G-USXGMII Serdes can support 100 100M ports, 10 1G ports, and so on. But I’m skeptical. If this is true, could anyone comment on whether the upstream MTK drivers would allow “pass through” (for lack of a better word) of the USXGMII signaling so a connected chip could be managed by the vendor’s driver?

Thanks in advance.