Example for blinking LED with PWM

1. We need a PWM driver in U-boot to control hardware.

submitted patch:

https://patchwork.ozlabs.org/patch/1242081/

https://patchwork.ozlabs.org/patch/1242083/

2. We need to enable PWM in dts and configure pinctrl

diff --git a/arch/arm/dts/mt7622-rfb.dts b/arch/arm/dts/mt7622-rfb.dts

index 05502bddec..165496e8d9 100644

--- a/arch/arm/dts/mt7622-rfb.dts

+++ b/arch/arm/dts/mt7622-rfb.dts

@@ -69,6 +69,13 @@

};

};

+ pwm_pins: pwm1 {

+ mux {

+ function = "pwm";

+ groups = "pwm_ch1_0" ;

+ };

+ };

+

watchdog_pins: watchdog-default {

mux {

function = "watchdog";

@@ -155,6 +162,12 @@

status = "okay";

};

+&pwm {

+ pinctrl-names = "default";

+ pinctrl-0 = <&pwm_pins>;

+ status = "okay";

+};

+

&mmc0 {

pinctrl-names = "default";

pinctrl-0 = <&mmc0_pins_default>;

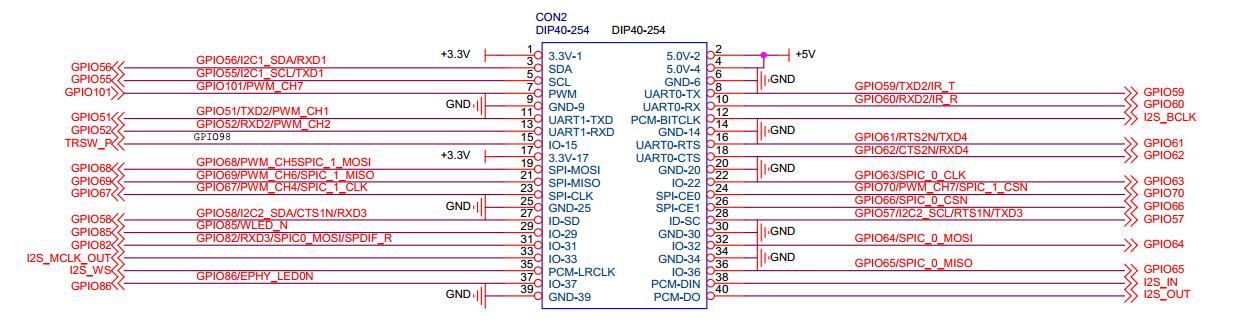

In this example, we use bpir64 pin 11 (UART1-TXD/GPIO51/TXD2/PWM_CH1) as PWM channel 1 (pwm_id=0), and connect this pin to a LED.

3. We need an application to access u-boot PWM API as a u-boot command

pwm 0 config 1000000000 500000000

pwm 0 enable

LED on (0.5 seconds) --> LED off (0.5 seconds) --> LED on (0.5 seconds) --> …

diff --git a/cmd/pwm.c b/cmd/pwm.c

new file mode 100644

index 0000000000..efd2f4590d

--- /dev/null

+++ b/cmd/pwm.c

@@ -0,0 +1,52 @@

+// SPDX-License-Identifier: GPL-2.0+

+/*

+ * Copyright (C) 2020 MediaTek Inc.

+ *

+ * Author: Sam Shih <[email protected]>

+ */

+

+#include <common.h>

+#include <command.h>

+#include <dm.h>

+#include <pwm.h>

+#include <dm/uclass-internal.h>

+

+int do_pwm(cmd_tbl_t *cmdtp, int flag, int argc, char * const argv[])

+{

+ struct udevice *dev;

+ unsigned long pwm_id, period, duty;

+

+ if (uclass_get_device(UCLASS_PWM, 0, &dev)) {

+ printf("unable to find pwm driver\n");

+ return CMD_RET_FAILURE;

+ }

+ if (argc < 2)

+ return CMD_RET_USAGE;

+ pwm_id = simple_strtoul(argv[1], NULL, 0);

+

+ if (strncmp(argv[2], "config", 10) == 0) {

+ if (argc < 4)

+ return CMD_RET_USAGE;

+ period = simple_strtoul(argv[3], NULL, 0);

+ duty = simple_strtoul(argv[4], NULL, 0);

+ if (pwm_set_config(dev, pwm_id, period, duty)) {

+ printf("unable to config pwm driver\n");

+ return CMD_RET_FAILURE;

+ }

+ }

+ else if (strncmp(argv[2], "enable", 10) == 0) {

+ pwm_set_enable(dev, pwm_id, true);

+ }

+ else if (strncmp(argv[2], "disable", 10) == 0) {

+ pwm_set_enable(dev, pwm_id, false);

+ }

+

+ return 0;

+}

+

+U_BOOT_CMD(

+ pwm, 5, 1, do_pwm,

+ "manage PWMs\n",

+ "<pwm_id> [config|enable|disable]\n"

+ "config: <pwm_id> config <period_in_ns> <duty_in_ns>\n"

+ "enable: <pwm_id> enable\n"

+ "disable: <pwm_id> disable\n"

+);