Hi, ( Solved but still interesting and useful for others )

Using OpenWRT master build,

I’m attempting to use the m.2 slot for a PCIe WLAN radio ( using a KEY-M/B converter card like this one : https://www.aliexpress.com/i/1005004195101734.html ).

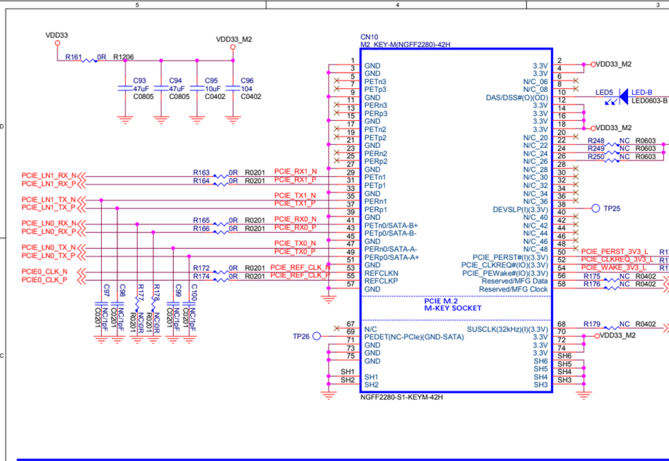

following the KEY-M pinout from here : https://pinoutguide.com/visual/gen/M.2_NGFF_connector.jpg , and the BPI-R3 schematic, I verified that CONFIG1 is left floating ( selecting PCIe mode instead of SATA mode )

.

.

It seems the PCIe bus does not come up when I use the converter card:

root@OpenWrt:/# dmesg | grep pci [ 0.045141] mtk-pcie-gen3 11280000.pcie: host bridge /soc/pcie@11280000 ranges: [ 0.045160] mtk-pcie-gen3 11280000.pcie: Parsing ranges property... [ 0.045169] mtk-pcie-gen3 11280000.pcie: MEM 0x0020000000..0x002fffffff -> 0x0020000000 [ 0.045242] phy phy-soc:[email protected]: pcie auto load valid efuse: ENABLE with value: 1 [ 0.045313] /soc/pcie@11280000: Failed to get clk index: 0 ret: -517 [ 0.045323] mtk-pcie-gen3 11280000.pcie: failed to get clocks [ 1.081380] mtk-pcie-gen3 11280000.pcie: host bridge /soc/pcie@11280000 ranges: [ 1.088715] mtk-pcie-gen3 11280000.pcie: Parsing ranges property... [ 1.094969] mtk-pcie-gen3 11280000.pcie: MEM 0x0020000000..0x002fffffff -> 0x0020000000 [ 1.111527] phy phy-soc:[email protected]: pcie auto load valid efuse: ENABLE with value: 1 [ 1.360525] mtk-pcie-gen3 11280000.pcie: PCIe link down, ltssm reg val: 0x1 [ 1.367527] mtk-pcie-gen3: probe of 11280000.pcie failed with error -110

Then I tested with some NVME modules… using an ADATA SU650 M.2 2280 SATA SSD ( I checked that CONFIG1 is linked to GND for SATA mode), I get the same output

[ 0.045909] mtk-pcie-gen3 11280000.pcie: host bridge /soc/pcie@11280000 ranges: [ 0.045929] mtk-pcie-gen3 11280000.pcie: Parsing ranges property... [ 0.045939] mtk-pcie-gen3 11280000.pcie: MEM 0x0020000000..0x002fffffff -> 0x0020000000 [ 0.046014] phy phy-soc:[email protected]: pcie auto load valid efuse: ENABLE with value: 1 [ 0.046092] /soc/pcie@11280000: Failed to get clk index: 0 ret: -517 [ 0.046102] mtk-pcie-gen3 11280000.pcie: failed to get clocks [ 1.083403] mtk-pcie-gen3 11280000.pcie: host bridge /soc/pcie@11280000 ranges: [ 1.090728] mtk-pcie-gen3 11280000.pcie: Parsing ranges property... [ 1.096981] mtk-pcie-gen3 11280000.pcie: MEM 0x0020000000..0x002fffffff -> 0x0020000000 [ 1.113557] phy phy-soc:[email protected]: pcie auto load valid efuse: ENABLE with value: 1 [ 1.352125] mtk-pcie-gen3 11280000.pcie: PCIe link down, ltssm reg val: 0x1 [ 1.359122] mtk-pcie-gen3: probe of 11280000.pcie failed with error -110

But When I use a SATA NVME ( Trancend PCIe SSD 110S ) I get successful bus startup :

root@OpenWrt:/# dmesg | grep pci [ 0.045057] mtk-pcie-gen3 11280000.pcie: host bridge /soc/pcie@11280000 ranges: [ 0.045077] mtk-pcie-gen3 11280000.pcie: Parsing ranges property... [ 0.045087] mtk-pcie-gen3 11280000.pcie: MEM 0x0020000000..0x002fffffff -> 0x0020000000 [ 0.045158] phy phy-soc:[email protected]: pcie auto load valid efuse: ENABLE with value: 1 [ 0.045233] /soc/pcie@11280000: Failed to get clk index: 0 ret: -517 [ 0.045242] mtk-pcie-gen3 11280000.pcie: failed to get clocks [ 1.078603] mtk-pcie-gen3 11280000.pcie: host bridge /soc/pcie@11280000 ranges: [ 1.085912] mtk-pcie-gen3 11280000.pcie: Parsing ranges property... [ 1.092194] mtk-pcie-gen3 11280000.pcie: MEM 0x0020000000..0x002fffffff -> 0x0020000000 [ 1.108758] phy phy-soc:[email protected]: pcie auto load valid efuse: ENABLE with value: 1 [ 1.274438] mtk-pcie-gen3 11280000.pcie: set MEM trans window[0]: cpu_addr = 0x20000000, pci_addr = 0x20000000, size = 0x10000000 [ 1.290248] mtk-pcie-gen3 11280000.pcie: PCI host bridge to bus 0000:00 [ 1.313188] pci_bus 0000:00: root bus resource [bus 00-ff] [ 1.329233] pci_bus 0000:00: root bus resource [mem 0x20000000-0x2fffffff] [ 1.343369] pci_bus 0000:00: scanning bus [ 1.354159] pci 0000:00:00.0: [14c3:1f32] type 01 class 0x060400 [ 1.360180] pci 0000:00:00.0: reg 0x10: [mem 0x00000000-0x00007fff 64bit] [ 1.367015] pci 0000:00:00.0: PME# supported from D0 D3hot D3cold [ 1.373095] pci 0000:00:00.0: PME# disabled [ 1.378078] pci_bus 0000:00: fixups for bus [ 1.382247] pci 0000:00:00.0: scanning [bus 00-00] behind bridge, pass 0 [ 1.388936] pci 0000:00:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring [ 1.396923] pci 0000:00:00.0: scanning [bus 00-00] behind bridge, pass 1 [ 1.403667] pci_bus 0000:01: scanning bus [ 1.407701] pci 0000:01:00.0: [126f:2263] type 00 class 0x010802 [ 1.413716] pci 0000:01:00.0: reg 0x10: [mem 0x00000000-0x00003fff 64bit] [ 1.420685] pci 0000:01:00.0: 8.000 Gb/s available PCIe bandwidth, limited by 5.0 GT/s PCIe x2 link at 0000:00:00.0 (capable of 31.504 Gb/s with 8.0 GT/s PCIe x4 link) [ 1.436291] pci_bus 0000:01: fixups for bus ...

I think the failure is because the clock pins are not connected between the NGFF slot and the "MSATA PCIe " slot by my converter board. ( following an MSATA pinout from here : Mini-SATA (mSATA) connector pinout diagram @ pinoutguide.com )

When I orderd the converters I failed to notice " The connector is similar in appearance to a PCI Express Mini Card interfacebut is not electrically compatible; the data signals need a connection to the SATA host controller instead of the PCI Express host controller. "