Sorry, did it like in your second example…i try the first one tomorrow

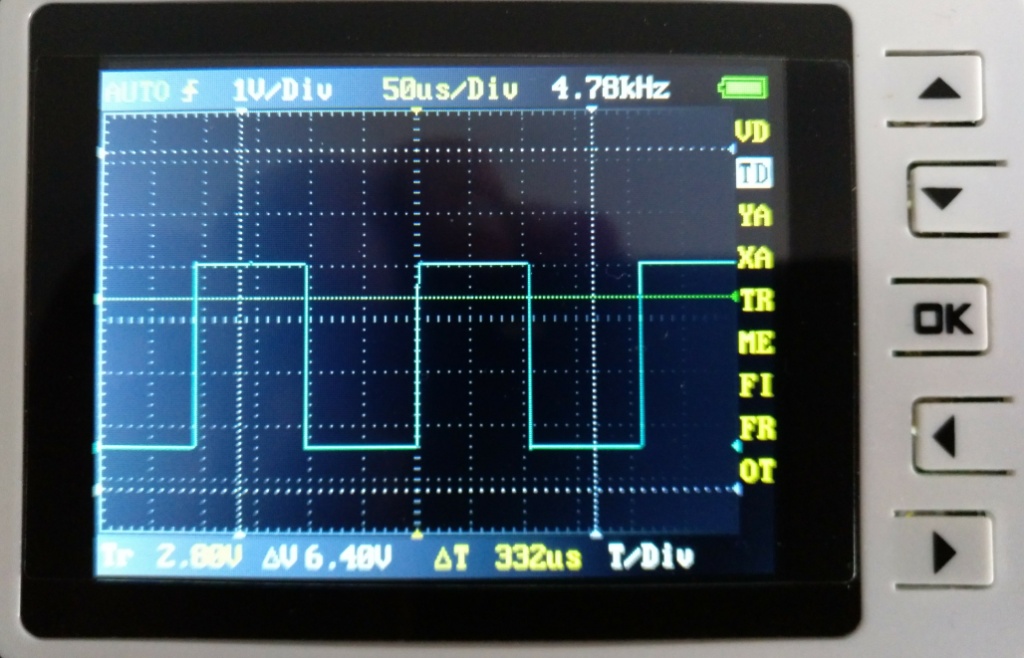

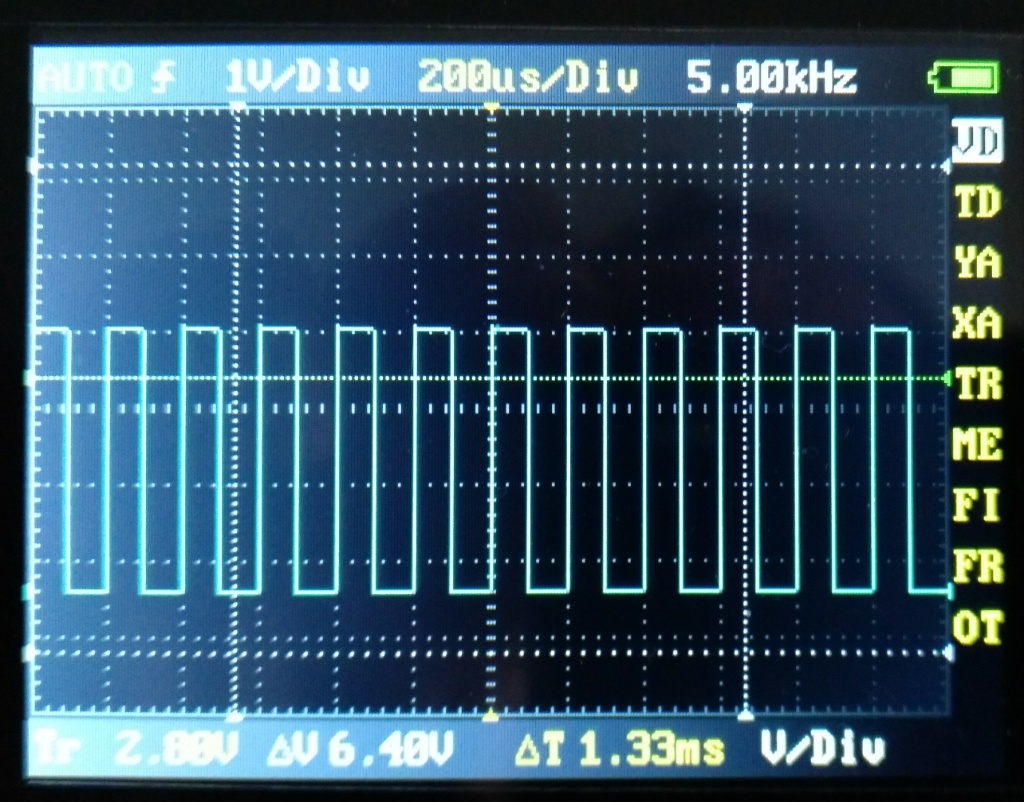

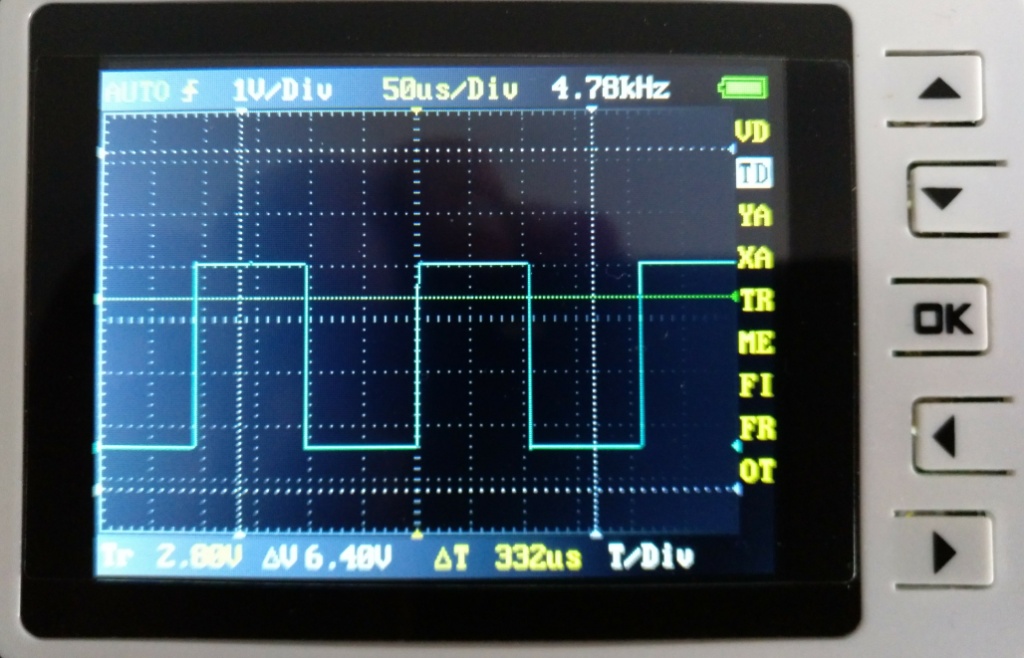

Edit: its more near 5kHz

How preceise should it be?

[ 73.950379] [mtk_pwm_config] clock: 68250000, clockrate: 273000000

[ 73.950390] [mtk_pwm_config] period_ns: 200000, duty_ns: 0

[ 73.950396] [mtk_pwm_config] resolution: 28, clkdiv: 1

[ 76.910445] [mtk_pwm_config] clock: 68250000, clockrate: 273000000

[ 76.910455] [mtk_pwm_config] period_ns: 200000, duty_ns: 100000

diff (added alternative calculation without additional variable) :

diff --git a/drivers/pwm/pwm-mediatek.c b/drivers/pwm/pwm-mediatek.c

index 1cc2f68..5aa6c4f 100644

--- a/drivers/pwm/pwm-mediatek.c

+++ b/drivers/pwm/pwm-mediatek.c

@@ -121,13 +121,18 @@ static int mtk_pwm_config(struct pwm_chip *chip, struct pwm_device *pwm,

struct mtk_pwm_chip *pc = to_mtk_pwm_chip(chip);

struct clk *clk = pc->clks[MTK_CLK_PWM1 + pwm->hwpwm];

u32 resolution, clkdiv = 0;

+ ulong clock;

int ret;

ret = mtk_pwm_clk_enable(chip, pwm);

if (ret < 0)

return ret;

- resolution = NSEC_PER_SEC / clk_get_rate(clk);

+ clock=clk_get_rate(clk) / 4;

+ printk(KERN_NOTICE "[mtk_pwm_config] clock: %lu, clockrate: %lu",clock,clk_get_rate(clk));

+

+ //resolution = NSEC_PER_SEC / ( clk_get_rate(clk) / 4 );

+ resolution = NSEC_PER_SEC / clock;

while (period_ns / resolution > 8191) {

resolution *= 2;

…

[20:43] root@bpi-r2:~# echo 100000 >/sys/class/pwm/pwmchip0/pwm3/period

[20:45] root@bpi-r2:~# echo 50000 >/sys/class/pwm/pwmchip0/pwm3/duty_cycle

is 9.55kHz

[20:45] root@bpi-r2:~# echo 1000000 >/sys/class/pwm/pwmchip0/pwm3/period

[20:46] root@bpi-r2:~# echo 500000 >/sys/class/pwm/pwmchip0/pwm3/duty_cycle

is 955 Hz

[20:47] root@bpi-r2:~# echo 10000000 >/sys/class/pwm/pwmchip0/pwm3/period

[20:50] root@bpi-r2:~# echo 5000000 >/sys/class/pwm/pwmchip0/pwm3/duty_cycle

95.5 Hz

so the clock(-divider) is a bit inaccurately…can you confirm, that these values are correct depending on Hardware-spec:

clock: 68250000, clockrate: 273000000