You could use my debian/ubuntu image and update kernel to 5.18-main with your own options from my git repo as first exercise

I have similar problem with dsa network speed 100Mbit: from r2pro to other server ~600Mbits from other server to r2pro = 100Mbits

Just adding: LAN-2-LAN (in bridge) works at full speed.

LAN-2-host and host-2-LAN about the same speeds 100/400

P.S.

R2 pro has the next tc rule which is absent in R2, or my PC:

bpi-r2pro ~ # tc qdisc show dev eth1

qdisc mq 0: root

qdisc fq 0: parent :1 limit 10000p flow_limit 100p buckets 1024 orphan_mask 1023 quantum 3036b initial_quantum 15180b low_rate_threshold 550Kbit refill_delay 40ms timer_slack 10us horizon 10s horizon_drop

Does anyone have a similar?

Look for the top 2 commits here:

https://github.com/frank-w/BPI-R2-4.14/commits/5.19-r2pro-pcie-mainline

These fixing the issue. The WIP One fixes the issue,second reverts a part i don’t want to change (sgmii)…maybe phy reset is needed as i get full speed,but first round of iperf3 gets many retransmitts

The problem is not traffic shaping (tc rule) as ethtool on eth1 shows only mii mode (100mbit). So the problem is from lan-ports over switch to eth1 (gmac). If you measure traffic from cpu to wan (eth0) you have no issue.

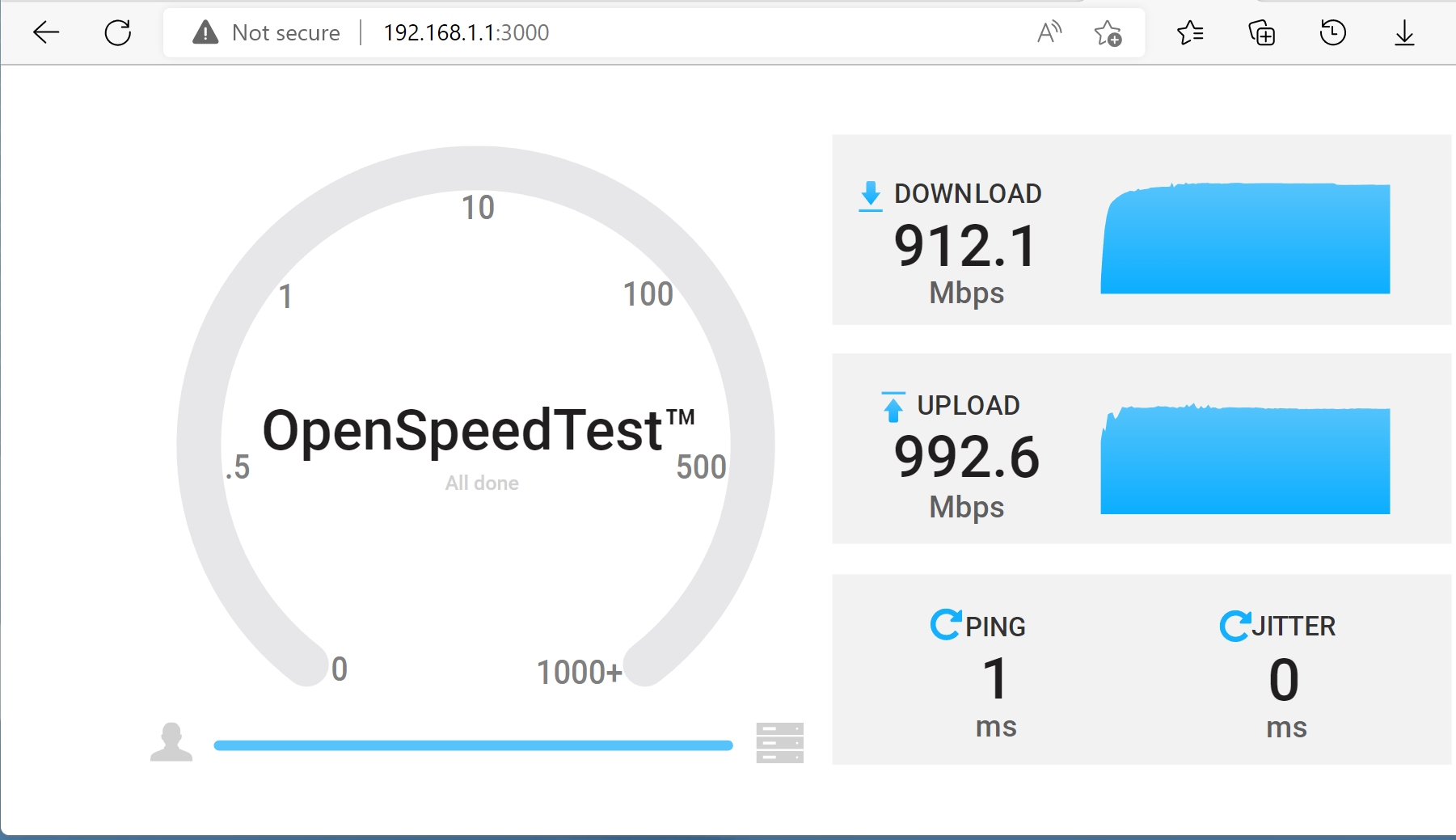

seems fixed: ~940mbit/s to r2pro ~660mbit/s from r2pro

have you applied both patches or only 1? 660 are not the best but maybe caused by retransmitts in first run of iperf

I use all your patches over 5.19

ok, you can drop my partial revert and you will see better traffic (if using only r2pro)…i try to nail down needed changes without breaking sgmii on p5 (because other devices may need it), but this can take some time.

Hm. seems last patch did’t change anything. I have ~600Mbit on one thread and 400-850Mbit/s with iperf3 -P5 option. But with last patch I did’t see any Retr and more stable speed for one transfer thread.

Strange…i had some retransmitts after reverting parts of the WIP patch. I guess phy reset is still needed

I’m testing the BPI R2 PRO on OpenWrt kernel 6.0-rc1, the 2 last patches fixed the mt7531 speed issue was getting 900-100, after applied the patches:

Tested, throughput has improved with the new patch.

~$ iperf3 -c 192.168.1.1

Connecting to host 192.168.1.1, port 5201

[ 5] local 192.168.1.222 port 41932 connected to 192.168.1.1 port 5201

[ ID] Interval Transfer Bitrate Retr Cwnd

[ 5] 0.00-1.00 sec 112 MBytes 941 Mbits/sec 0 537 KBytes

[ 5] 1.00-2.00 sec 113 MBytes 947 Mbits/sec 0 547 KBytes

[ 5] 2.00-3.00 sec 112 MBytes 940 Mbits/sec 0 566 KBytes

[ 5] 3.00-4.00 sec 111 MBytes 932 Mbits/sec 0 591 KBytes

[ 5] 4.00-5.00 sec 112 MBytes 941 Mbits/sec 0 591 KBytes

[ 5] 5.00-6.00 sec 112 MBytes 941 Mbits/sec 0 591 KBytes

[ 5] 6.00-7.00 sec 112 MBytes 942 Mbits/sec 0 591 KBytes

[ 5] 7.00-8.00 sec 111 MBytes 935 Mbits/sec 0 591 KBytes

[ 5] 8.00-9.00 sec 112 MBytes 942 Mbits/sec 0 591 KBytes

[ 5] 9.00-10.00 sec 111 MBytes 934 Mbits/sec 0 591 KBytes

- - - - - - - - - - - - - - - - - - - - - - - - -

[ ID] Interval Transfer Bitrate Retr

[ 5] 0.00-10.00 sec 1.09 GBytes 940 Mbits/sec 0 sender

[ 5] 0.00-10.01 sec 1.09 GBytes 937 Mbits/sec receiver

iperf Done.I’m having trouble with the M.2 slot not detecting any card on 6.0, the Mini PCIe works ok.

root@OpenWrt:~# lspci

0001:00:00.0 PCI bridge: Rockchip Electronics Co., Ltd RK3568 Remote Signal Processor (rev 01)

0002:00:00.0 PCI bridge: Rockchip Electronics Co., Ltd RK3568 Remote Signal Processor (rev 01)

0002:01:00.0 Network controller: Qualcomm Atheros AR93xx Wireless Network Adapter (rev 01)

[ 0.172615] rockchip-snps-pcie3-phy fe8c0000.phy: failed to find rockchip,pipe_grf regmap

[ 0.175671] shpchp: Standard Hot Plug PCI Controller Driver version: 0.4

[ 0.439439] phy phy-fe8c0000.phy.7: lane number 0, val 1

[ 0.439976] phy phy-fe8c0000.phy.7: lane number 1, val 2

[ 0.440499] phy phy-fe8c0000.phy.7: bifurcation enabled

[ 0.441116] rockchip-dw-pcie 3c0400000.pcie: host bridge /pcie@fe270000 ranges:

[ 0.441867] rockchip-dw-pcie 3c0400000.pcie: IO 0x037ef00000..0x037effffff -> 0x003ef00000

[ 0.442774] rockchip-dw-pcie 3c0400000.pcie: MEM 0x0340000000..0x037eefffff -> 0x0000000000

[ 0.452980] rockchip-dw-pcie 3c0400000.pcie: iATU unroll: enabled

[ 0.453585] rockchip-dw-pcie 3c0400000.pcie: iATU regions: 8 ob, 8 ib, align 64K, limit 8G

[ 1.559526] rockchip-dw-pcie 3c0400000.pcie: Phy link never came up

[ 1.560270] rockchip-dw-pcie 3c0400000.pcie: PCI host bridge to bus 0001:00

[ 1.560960] pci_bus 0001:00: root bus resource [bus 00-0f]

[ 1.561508] pci_bus 0001:00: root bus resource [io 0x0000-0xfffff] (bus address [0x3ef00000-0x3effffff])

[ 1.562448] pci_bus 0001:00: root bus resource [mem 0x340000000-0x37eefffff] (bus address [0x00000000-0x3eefffff])

[ 1.563529] pci 0001:00:00.0: [1d87:3566] type 01 class 0x060400

[ 1.564151] pci 0001:00:00.0: reg 0x38: [mem 0x340000000-0x34000ffff pref]

[ 1.564900] pci 0001:00:00.0: supports D1 D2

[ 1.565325] pci 0001:00:00.0: PME# supported from D0 D1 D3hot

[ 1.570612] pci_bus 0001:01: busn_res: can not insert [bus 01-ff] under [bus 00-0f] (conflicts with (null) [bus 00-0f])

[ 1.571840] pci 0001:00:00.0: BAR 6: assigned [mem 0x340000000-0x34000ffff pref]

[ 1.572576] pci 0001:00:00.0: PCI bridge to [bus 01-ff]

[ 1.574830] pcieport 0001:00:00.0: PME: Signaling with IRQ 26

[ 1.575779] pcieport 0001:00:00.0: AER: enabled with IRQ 26

[ 1.632857] rockchip-dw-pcie 3c0800000.pcie: host bridge /pcie@fe280000 ranges:

[ 1.633617] rockchip-dw-pcie 3c0800000.pcie: IO 0x03bef00000..0x03beffffff -> 0x003ef00000

[ 1.634495] rockchip-dw-pcie 3c0800000.pcie: MEM 0x0380000000..0x03beefffff -> 0x0000000000

[ 1.645076] rockchip-dw-pcie 3c0800000.pcie: iATU unroll: enabled

[ 1.645681] rockchip-dw-pcie 3c0800000.pcie: iATU regions: 8 ob, 8 ib, align 64K, limit 8G

[ 1.852688] rockchip-dw-pcie 3c0800000.pcie: PCIe Gen.1 x1 link up

[ 1.853425] rockchip-dw-pcie 3c0800000.pcie: PCI host bridge to bus 0002:00

[ 1.854114] pci_bus 0002:00: root bus resource [bus 00-0f]

[ 1.854661] pci_bus 0002:00: root bus resource [io 0x100000-0x1fffff] (bus address [0x3ef00000-0x3effffff])

[ 1.855624] pci_bus 0002:00: root bus resource [mem 0x380000000-0x3beefffff] (bus address [0x00000000-0x3eefffff])

[ 1.856698] pci 0002:00:00.0: [1d87:3566] type 01 class 0x060400

[ 1.857310] pci 0002:00:00.0: reg 0x10: [mem 0x00000000-0x3fffffff]

[ 1.857934] pci 0002:00:00.0: reg 0x14: [mem 0x00000000-0x3fffffff]

[ 1.858556] pci 0002:00:00.0: reg 0x38: [mem 0x380000000-0x38000ffff pref]

[ 1.859325] pci 0002:00:00.0: supports D1 D2

[ 1.859752] pci 0002:00:00.0: PME# supported from D0 D1 D3hot

[ 1.864979] pci_bus 0002:01: busn_res: can not insert [bus 01-ff] under [bus 00-0f] (conflicts with (null) [bus 00-0f])

[ 1.866187] pci 0002:01:00.0: [168c:0030] type 00 class 0x028000

[ 1.866908] pci 0002:01:00.0: reg 0x10: [mem 0x380000000-0x38001ffff 64bit]

[ 1.867779] pci 0002:01:00.0: reg 0x30: [mem 0x380000000-0x38000ffff pref]

[ 1.868871] pci 0002:01:00.0: supports D1 D2

[ 1.869315] pci 0002:01:00.0: PME# supported from D0 D1 D2 D3hot D3cold

[ 1.879431] pci 0002:00:00.0: BAR 0: no space for [mem size 0x40000000]

[ 1.880091] pci 0002:00:00.0: BAR 0: failed to assign [mem size 0x40000000]

[ 1.880778] pci 0002:00:00.0: BAR 1: no space for [mem size 0x40000000]

[ 1.881429] pci 0002:00:00.0: BAR 1: failed to assign [mem size 0x40000000]

[ 1.882116] pci 0002:00:00.0: BAR 8: assigned [mem 0x380000000-0x3800fffff]

[ 1.882828] pci 0002:00:00.0: BAR 6: assigned [mem 0x380100000-0x38010ffff pref]

[ 1.883565] pci 0002:01:00.0: BAR 0: assigned [mem 0x380000000-0x38001ffff 64bit]

[ 1.884356] pci 0002:01:00.0: BAR 6: assigned [mem 0x380020000-0x38002ffff pref]

[ 1.885085] pci 0002:00:00.0: PCI bridge to [bus 01-ff]

[ 1.885604] pci 0002:00:00.0: bridge window [mem 0x380000000-0x3800fffff]

[ 1.887974] pcieport 0002:00:00.0: PME: Signaling with IRQ 28

[ 1.888937] pcieport 0002:00:00.0: AER: enabled with IRQ 28i cannot test the m.2 but afaik it is a key-e so maybe it recognizes only 3g/4g/5g cards, i’m no expert in m.2 functions

does it work in 5.19? maybe the pinctrl is wrong…you can try reverting the pinctrl patch

Which card have you inserted (vendor,type/partno)?

Can you test with bpi kernel (5.10/4.19) to check for hw issue?

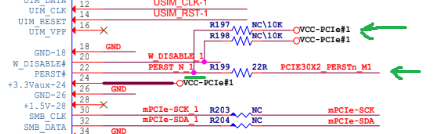

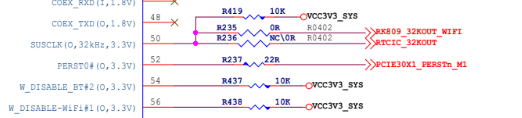

In the schematics pdf, on the page 18, the M2 scheme indicates that PCIE30X1 lanes are connected.

I’ve tested M2 slon with MT7912 wifi+bt card on 5.18 and 6.0-rc, both can’t detect the card. But i didn’t tested it with BSP kernel.

Also from schematics:

P17: minipcie

P18: M2

I’m not a PCIE professional, but may it be the reason?

i’m not sure whats your point here…

for power there is a general regulator for clock (vcc3v3_pi6c_05:gpio0 RK_PD4), then regulators for each port (vcc3v3_minipcie:gpio0 RK_PC6, vcc3v3_ngff:gpio4 RK_PC1)

&pcie3x1 is m.2 slot and &pcie3x2 is pcie in dts…so this does match schematic too. Both are only 1 lane splitted to 2 virtual controllers.

was 5.18 working? 5.18 had bifurcation in pcie-driver, then peter moved it to phy driver

No, it wasnt (for M2)

MY point is:

googled:

Once the EP detects that the #PERST is asserted, it is an indication to EP that the RC provided power and clock are stable and EP side can start initialization on the device for PCIe linkup.

None: RC - Root Complex/host ;EP - End Point/Device

I don’t know how the #PERST is managed: by PCIE controller, by driver, by dts or somehow else. In miniPCIE it’s pulled to VCC-PCIe (like always on?), on M2 it’s not.

I fixed the M.2 slot, issue was incorrect gpio pin in vcc_3v3_ngff.

root@OpenWrt:~# lspci

0001:00:00.0 PCI bridge: Rockchip Electronics Co., Ltd RK3568 Remote Signal Processor (rev 01)

0001:01:00.0 Network controller: MEDIATEK Corp. Device 7922

0002:00:00.0 PCI bridge: Rockchip Electronics Co., Ltd RK3568 Remote Signal Processor (rev 01)

0002:01:00.0 Network controller: Qualcomm Atheros AR93xx Wireless Network Adapter (rev 01)

Just curiosity, where did you get info on correct gpio?

Thanks

Just curiosity, where did you get info on correct gpio?

Thanks

I Got it, PB7 - the same as in BSP